ASIC/FPGA

Overview

Mobiveil’s ASIC Services group possess deep expertise in CXL, SSD Storage and Hybrid Memory systems. This expertise coupled with reusable SOC blocks and verification components makes Mobiveil an ideal business partner in accelerating customer ASIC development cycle.

Additionally flexible business models offers choice for customer to pick and choose the right one, which suits them.

Services Offered

Offshore Development Center (ODC)

- Experience running several ASIC Design/Verification/PD & FPGA Solution ODCs for multi-year, ranging from 10-35 engineers

- Dedicated Program Management

- All round in house expertise to independently manage design or verification or PD effort

- Ability to quickly ramp up and provide a minimum risk execution model

- Physical and Network Isolation

Turnkey Services

- SoC frontend Design and verification

- Complex FPGA solutions

- FPGA based ASIC Testers

- IP level verification & VIP development

- Structured ASIC Migration

Specialized Domains

- CXL based SOC Design/Verification

- SSD SOCs Design/Verification

- Hybrid Memory Design and Verification (DDR4 NV-DIMMs)

- High Speed Protocol Verification (CXL 2.0, PCIe Gen5, USB 3.0, SRIO)

- IP level verification (LPDDR4, DDR4, DDR3, I3C)

Reusable SOC Components

- Jedec xSPI Controller

- PSRAM Controller

- HyperFlash controller

- AXI Interconnect Matrix

- AXI-APB bridge

- SRIO BFM

Staff Augmentation

- Supporting all major semiconductor companies in all aspects of ASIC flow

- Geographies - USA, India and China

Key Project Delivered

RISC-V based SOC – Spec2Netlist

DDR4 NV-DIMM Design (SATA based)

DDR4 NV-DIMM Design (PCIe based)

NVMe/PCIe SSD SOC Verification

PCIe Gen4 Switch based SSD Tester

DDR4 based AI Chip tester

Octal SPI based AI Chip tester

NVMe VIP development

USB 3.0 Host Verification

LPDDR4/DDRx IP Verification

IP Licensing – PSRAM Controller, Hyperbus controller, AXI Interconnect Matrix

Methodology

Design

Mobiveil follows a robust in-house design guidelines that addresses both ASIC and FPGA needs. The guideline accounts for Synthesis/DFT friendly and Low Power designs. Process-wise, the guidelines takes into account, the handshake required with different teams like PD, DFT, Verification and Validation. A separate Lint and CDC process guideline enable designers to deliver a first time right design.

Verification

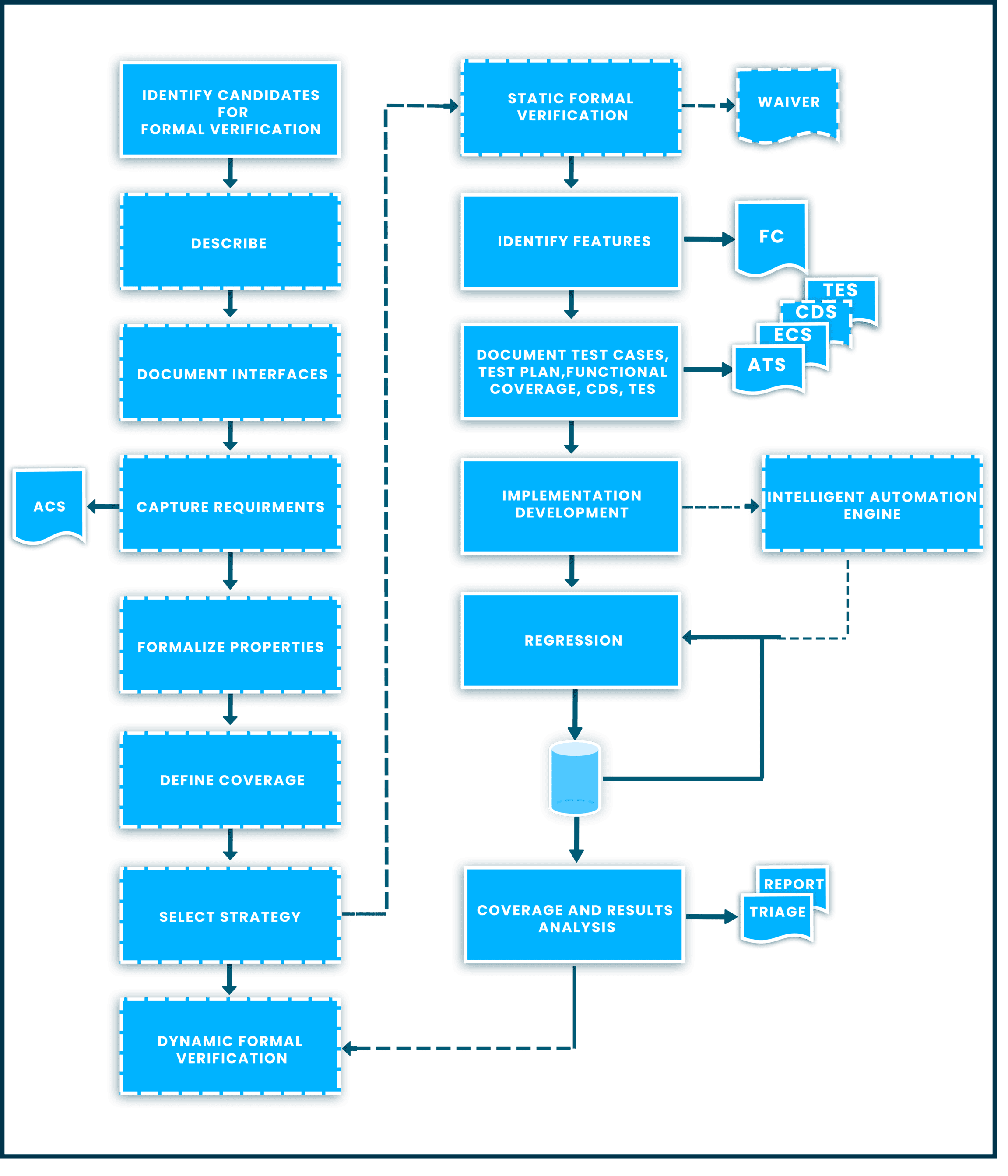

Mobiveil uses state of the art methodologies/technologies and tools for verification and achieve working silicon first time with its very thorough verification process from spec to sign off. Our team has extensive expertise in full chip verification, IP level verification, subsystem level verification in SV/UVM. We have expertise in developing self-checking Testbench Environments, BFMs, and using third party VIPs (Cadence, Mentor, Avery…). Our team has expertise in constrained random, assertion based, coverage driven, formal, and gate level verification. We ensure before sign off we meet coverage goals. Mobiveil has expertise in Design and Verification ODCs, executing turn key projects, and has expertise in verifying IPs, Subsystems, and SoCs.

Methodology

| Design | Verification |

|---|---|

| Mobiveil follows a robust in-house design guidelines that addresses both ASIC and FPGA needs. The guideline accounts for Synthesis/DFT friendly and Low Power designs. Process-wise, the guidelines takes into account, the handshake required with different teams like PD, DFT, Verification and Validation. A separate Lint and CDC process guideline enable designers to deliver a first time right design. | Mobiveil uses state of the art methodologies/technologies and tools for verification and achieve working silicon first time with its very thorough verification process from spec to sign off. Our team has extensive expertise in full chip verification, IP level verification, subsystem level verification in SV/UVM. We have expertise in developing self-checking Testbench Environments, BFMs, and using third party VIPs (Cadence, Mentor, Avery…). Our team has expertise in constrained random, assertion based, coverage driven, formal, and gate level verification. We ensure before sign off we meet coverage goals. Mobiveil has expertise in Design and Verification ODCs, executing turn key projects, and has expertise in verifying IPs, Subsystems, and SoCs. |