Winbond HyperRAM

Overview

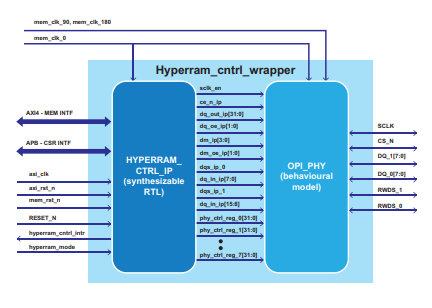

Mobiveil’s HyperRAMTM controller supports Winbond’s HyperBus

based HyperRAMTM devices which are used in following applications:

- IoT

- Consumer devices

- Automotive

- Industrial

This controller enables smooth integration of Winbond’s HyperBus

HyperRAMTM memory chips into various new-gen SoCs’.

The controller is designed using Technology independent Verilog RTL and

supports all industry standard Simulator, Synthesis and Lint/CDC tools.

- Compatible with W958D6NW, W958D6NKY, W956x8MBYA, W955D8MBYA HyperRAMTM devices from Winbond

- 16 bit data bus - DQ[15:0] support for W958D6NW, W958D6NKY devices

- 8 bit data bus - DQ[7:0] support for W956x8MBYA/ W955D8MBYA devices

- Read-Write data strobe RWDS [1:0]

- Memory Clock rate upto 250 MHz

- AXI memory mapped system interface for memory access.

- APB port for control registers accesses

- Supports Linear Burst, Hybrid burst and Wrap burst

- Low power features like deep power down, Hybrid sleep mode are handled by the controller through a CSR register.

Design Attributes

• Highly modular and programmable design • Fully synchronous design • Software control for key featuresProduct Package

• RTL Code • System Verilog/UVM based Testbench • Test cases • Behavioral PHY Model • Validated FPGA PHY reference designDocumentation

• Data-sheet • Verification PlanLicensing Options

• Single Design or Multi-project license (Encrypted RTL or HDL Source Code)Get the Detailed Product Brief here

Winbond HyperRAM

Mobiveil’s HyperRAMTM controller supports Winbond’s HyperBus

based HyperRAMTM devices which are used in following applications:

- IoT

- Consumer devices

- Automotive

- Industrial

This controller enables smooth integration of Winbond’s HyperBus

HyperRAMTM memory chips into various new-gen SoCs’.

The controller is designed using Technology independent Verilog RTL and

supports all industry standard Simulator, Synthesis and Lint/CDC tools.