NVM EXPRESS

Overview

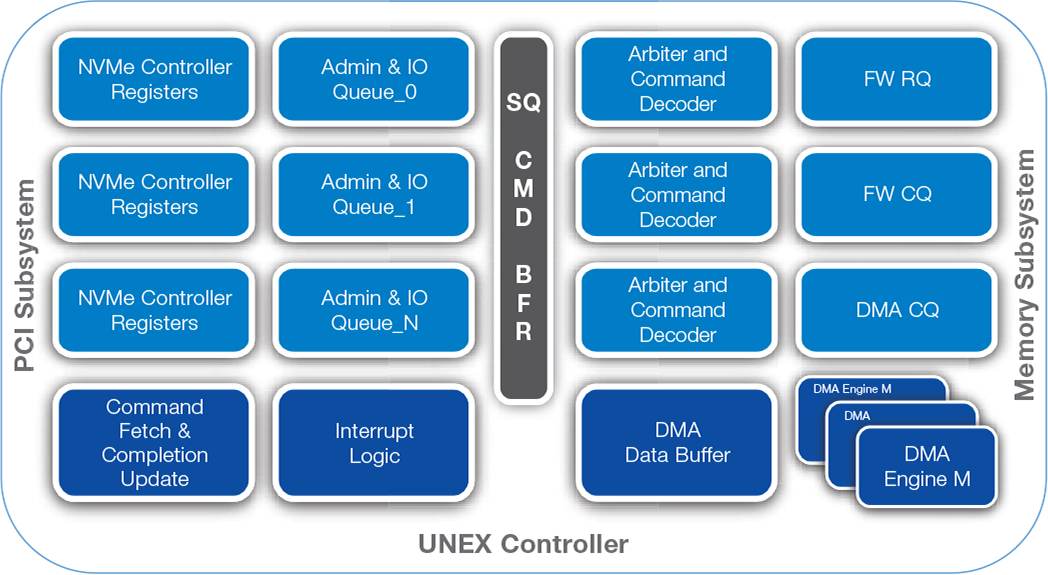

Mobiveil’s Universal NVM Express Controller (UNEX) is highly

flexible and configurable design targeted for both Enterprise

and client class solutions that unlock the current and future

potential of PCIe-based SSDs. The UNEX controller core

efficiently supports multi-core architectures ensuring thread(s)

may run on each core with their own queue and interrupt

without any locks required. It provides support for end-to-end

data protection, security and encryption as well as robust error

reporting and management capabilities. The controller architecture is carefully tailored to optimize link and throughput utilization, latency, reliability, power consumption and silicon

footprint.

Mobiveil’s UNEX controller can be used along with Mobiveil

LDPC, DDR4/3 (UMMC) and Enterprise Flash controller (EFC)

IPs for a complete NVMe/SSD implementation.

The UNEX controller comes with 2 flavors:

- UNEX Controller with AXI Control and Data path interfaces for easy adoption in an SoC implementation

- UNEX Controller with Streaming Control and Data path interface (AXI4 ST) for easy adoption in an SoC implementation with PCIe HIP or any third party PCIe Controllers

UNEX Controller design is independent of implementation tools

and target technology. Mobiveil solution allows the licensees to

easily migrate among FPGA, Gate array and Standard cell

technologies optimally.

- Compliance to NVM Express 2.3 Specification

- Compliant with AXI4-ST/AXI interface towards PCIe interface

- Compliant with AXI4 interface towards memory subsystem interface

- Internal data path width: 128/256/512 bit

- Host memory page size support of 128MB

- Supports Multiport configuration for Multipath IO

- Supports Multipath IO and namespace sharing capabilities

- Support for configurable number of IO queues

- Support for configurable queue depth

- Support for configurable number of DMA engines

- Support for round robin or weighted round robin with urgent priority arbitration mechanism

- Supports all optional admin commands

- Supports all optional NVM commands

- Efficient and streamlined command handling

- Well-defined command interface for local CPU to perform subsystem initialization and handle non-hardware tasks

- End-to-end data protection support

- E2E protection (16b / 32b / 64b) support

- Supports Zoned namespace command set and Key Value command set

- Supports copy command and lock command

Configurable Options

• Multi-port or Single Port • Inclusion / Exclusion of AXI / Streaming interface modules • Number of IO Queues • IO Queue Depth • Number of DMA Engines • Number of Non-Volatile Memory Channels • Data Path Widths (64, 128, 256, 512) • Data Buffer SizeDesign Attributes

• Highly modular and configurable design • Layered architecture • Fully synchronous design • Supports both sync and async reset • Software control for key features • Multiple loopbacks for debugProduct Package

• RTL Code • UVM-based test bench and behavioral models • Test cases • Protocol checkers and bus watchers • Configurable synthesis shellDocumentation

• Design Datasheet • Verification Guide • Synthesis GuideLicensing Option

• NVMe Controller (UNEX)Get the Detailed Product Brief here

OCTA PSRAM