LDPC

Overview

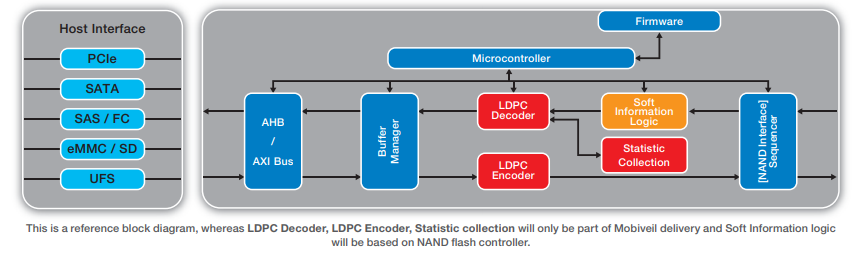

Mobiveil’s LDPC Encoder / Decoder* is a flash reliability solution delivering industry-leading flash endurance and retention through advanced LDPC error correction coupled with statistical digital signal processing (S-DSP) at the lowest power and smallest foot print. LDPC incorporates these advanced technology in to a highly scalable flash media side platform that can be tailored to customers specific application requirements from smart phones and tablets that require ultra-low power consumption to SSDs for enterprise computing applications that demand the highest performance.

- Patented technology delivers the industry’s highest reliability, highest performance, and lowest power for next-generation flash controllers

- Dramatic increases in P/E cycles significantly extends the life of flash memory

- Addresses the reliability challenges of MLC, TLC and 3D Flash at 1y and 1z nm geometries

- Access to flash manufacturer’s test mode commands to enable the generation of soft information for optimal reliability performance

- LDPC IP scalability

- Supporting a wide range of data-rates

- 50MB/s to 9.0GB/s for a single LDPC instance

- Scalable platform provides the basis for customer specific custom-LDPC cores

- Each LDPC IP is optimized for

- Codeword size, supports wide range of codewords

- Maximum amount of supported parity

- High degree of parallelism for high data-rate applications

- Different Memory access options

- Platform specific options (eASIC, FPGA, 40nm ASIC, 28nm ASIC, 16nm ASIC, 10nm ASIC)

- All LDPC IP Cores share the following features

- Simultaneous support for different amounts of parity

- Simultaneous support for several LDPC codes

- On-the-fly switching from one LDPC code to another

- Low area and power

- Patented technology delivers the industry's highest reliability, highest performance, and lowest power for next-generation flash controllers

- Dramatic increases in P/E cycles significantly extends the life of flash memory

- Addresses the reliability challenges of MLC, TLC and 3D Flash at 1y and 1z nm geometries

- Access to flash manufacturer's test mode commands to enable the generation of soft information for optimal reliability performance

Licensing Options

• LDPC • NVMe (UNEX) + LDPC + Enterprise Flash ControllerProduct Package

• Source Code for LDPC Compiler • Source Code for LDPC Matrix Generation Software • FPGA based LLR generation reference design with MATLAB interface • UVM verification env with encoder, error injector and decoder instantiatedDocumentation

• IP User Guide • Synthesis GuideGet the Detailed Product Brief here

OCTA PSRAM