Overview

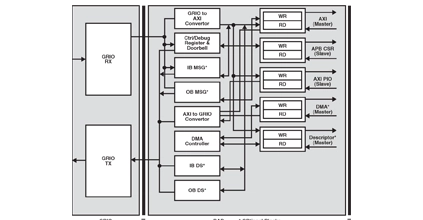

Mobiveil’s RapidlO-AXI Bridge (RIO-AXI Bridge) is a highly flexible and configurable IP used along with Mobiveil native RapidlO Controller (GRIO) to provide RapidlO interface on one side and AXI interface on

the system side. The Bridge has been architectured to interface with a RapidlO controller used as a Host or device. The RIO-AXI BRIDGE uses high speed multi-channel DMA Messaging and data streaming controllers to match the bandwidth requirements of the RIO solution.

The Mobiveil RIO-AXI Bridge is a simple, configurable and layered architecture, independent of applications, implementation tools or target technology. The controller architecture is carefully tailored to optimize latency, power consumption and silicon footprint, making it ideal for cost and performance sensitive applications. The RIO-AXI BRIDGE solution provides highly scalable bandwidth through a configurable data path width and clock frequency.

The controller’s simple, configurable and layered architecture is independent of application logic, PHY designs, implementation tools and most importantly the target technology. Mobiveil solution allows the licensees to easily migrate among FPGA Gate array and Standard cell technologies optimally. Its flexible backend interface makes it easy to be integrated into wide range of applications. Mobiveil solution provides highly scalable bandwidth through configurable lanes, widths and frequencies.

- Compliant with RapidlO specification, Revision 4.0

- Compliant to AMBA AXI protocol AXl3 / AXl4

- Supports 32-bit or 38 -bit or 64 bit AXI addressing

- AXI PIO operation with configurable number of AXI Slaves

- RPIO operation with configurable number of AXI Masters

- Multi-channel Read and Write DMA

- Message and Datastream

Features

• Serial and Parallel Interfaces supported • 1x, 2x and 4x serial interface • 64/128/256-bit internal data path • PBUS interface for configuration register access • Up to 256 bytes data payload • Hardware error recovery • Exhaustive error reporting and handling • Pass-Through mode of operation for RIO packets up to 288 bytes • Accept all Mode of operation for fall over supportConfigurable Options

• PIO, DMA, Message, Data streaming or mixed mode of operation • Parallel/Serial mode of operation • Bypass supportDesign Attributes

• Highly modular and configurable design • Layered architecture • Fully synchronous design • Supports both sync and async reset • Clearly demarked clock domains • Software control for key features • Multiple loop backs for debugProduct Package

• Configurable RTL Code • HDL based test bench and behavioral models • Test cases • Protocol checkers, bus watchers and performance monitors • Configurable synthesis shellDocumentation

• Design Guide • Verification Guide • Synthesis GuideGet the Detailed Product Brief here