DDR5

Overview

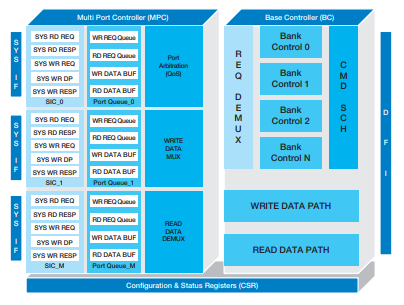

Mobiveil’s UMMC (Universal Multi-port Memory Controller for RLDRAM2/3, DDR5/4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2) is a highly flexible and configurable design that supports RLDRAM2, RLDRAM3 and JEDEC compliant DDR5, DDR4 3DS, DDR4, DDR3, LPDDR3, LPDDR3 and LPDDR2 memories. It is targeted for high bandwidth access and low power consumption such as next-generation mobile, networking and consumer applications. The controller architecture is carefully tailored to achieve reliable high-frequency operation with dynamic power management and rapid system debug capabilities.

- Compliant with AXI4 specification

- Compliant with DFI 3.1/ 5.1 Specification

- RLDRAM2/RLDRAM3 support and JEDEC compliant DDR3/DDR4/DDR5/LPDDR2/LPDDR3 support

- Supports memory data width from 8 to 64 bits for DDR3, DDR4, DDR5, LPDDR2 & LPDDR3 and x9, x18, x36 devices in any combined data width for RLDRAM2 & RLDRAM3

- Supports chip select interleaving

- Supports single and multi-port host buses AMBA4 AXI upto 32 ports

Features

• Supports multiple ranks • Supports 16/8/4 banks per rank • Configurable AXI address width • Configurable Request queue depth • Configurable Write and Read data FIFO size • Configurable QoS through various arbitration schemes • Supports following MC Clock to PHY Clock ratio - 1:1 (Full-rate Mode), 1:2 (Half-rate Mode), 1:4 (Quarter rate Mode) • Supports self-refresh and partial array self-refresh • Supports Auto-refresh, per-bank refresh and multi-bank refresh (RLDRAM) • Supports various power down modes - Active/Precharge/Deep power down • Supports Intelligent request scheduling • Maximizes bus efficiency through look-ahead command processing and bank-level parallelismDesign Attributes

• Highly modular and configurable design • Layered architecture • Fully synchronous design • Supports both sync and async reset • Clearly demarked clock domains • Software control for key featuresProduct Package

• Configurable RTL Code • HDL based test bench and behavioral models • Test cases • Protocol checkers, bus watchers and performance monitors • Configurable synthesis shellDocumentation

• Design Guide • Verification Guide • Synthesis GuideGet the Detailed Product Brief here