xSPI

Overview

- Supports low power EcoXiP family

of devices from ADESTO - Supports OctaFlash devices from

Macronix - Supports XccelaTM flash memory

from MICRON - Limited or full support of other

DDR-QUAD-SPI devices - Supports NOR Flash devices from Cypress (Infineon) including Semper family

- Supports Winbond QSPI NAND Flash and similar devices

- Winbond Octal NAND W35N04JWXXIC

- Winbond NAND W25N01GWxxIG

- Winbond NOR W25Q512JVxIQ

- Adesto AT25XP032

- Micron MT35XL256ABA

- Micron MT25QU01GBBB8E0 (x4)

- Macronix MX25UM51245G

- Cypress HyperFlash S26KL512S

- Cypress Semper S26HS01GT

- Supports Cypress Hyperram S27KL0643

- All similar devices in Market

- Complaint to JESD251A Specification

- Memory mapped access to the connected flash devices

- Continuous Burst transfer support

- Auto boot support

- XIP support

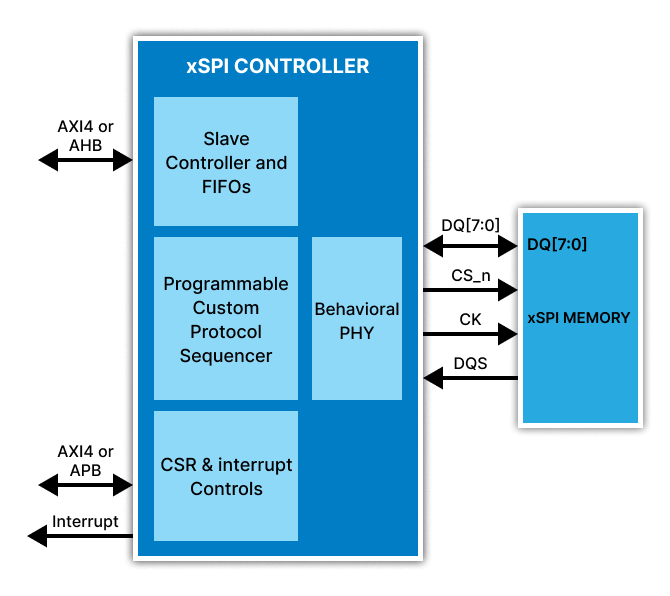

- AXI4 or AHB-Lite system interface for memory access with outstanding address support

- AXI4 or APB interface port for CSR register access

- Custom protocol Sequence based design to support an array of vendors

Design Attributes

• Highly modular and programmable design • Fully synchronous design • Software control for key featuresProduct Package

• RTL Code • System Verilog/UVM based Testbench • Test cases • Protocol checkers and bus watchersDocumentation

• Design Guide • Verification Guide • Synthesis GuideGet the Detailed Product Brief here

OCTA PSRAM