Overview

Mobiveil’s Bridge and Switch IP solutions are very popular with customers connecting PCIe or SRIO IP’s to AMBA/AXI Bridge with in their SoCs. A full PCI Express Switch is also available for customer implementation targeting unique PCI solutions requiring PCIe transparent switching functionality.

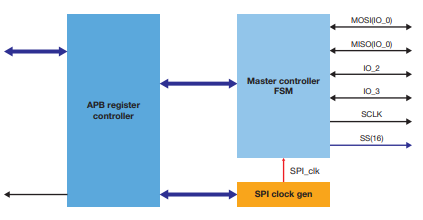

- Configurable SPI modes: • Standard SPI mode • Dual SPI mode • Quad SPI mode

- Standard/Dual/Quad SPI mode supports: • Single Master mode only • MSB first only

- Supports programmable SPI clocking modes

- Programmable interrupt on SPI-done

- SPI Slave devices can be independently selected

- Programmable Power-down mode for Master statemachine

- Programmable SCLK frequency derived from system clock

- Configurable Data FIFO depth

Differentiated Features

• Programmable request/response schemes like Transmit only, Receive only, Command-address-data, Address-data • Supports upto 32 bits of fullduplex transfer in standard mode • Independently programmable frame sizes for command, address and data • Programmable idle time between command, address and data • Register controlled slave_select assertion/deassertion during idle time • State machine status register for debugging • Supports upto 16 SlavesDesign Attributes

• Highly modular and programmable design • Fully synchronous design • Software control for key featuresProduct Package

• RTL Code • System Verilog/UVM based Testbench • Test cases • Protocol checkers and bus watchersDocumentation

• User GuideLicensing Options

• Single Design or Multi-project license (HDL Source Code/FPGA Netlist)Get the Detailed Product Brief here